114,99 €

Mehr erfahren.

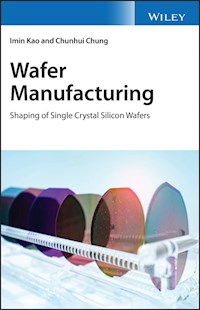

- Herausgeber: John Wiley & Sons

- Kategorie: Fachliteratur

- Sprache: Englisch

Presenting all the major stages in wafer manufacturing, from crystals to prime wafers.

This book first outlines the physics, associated metrology, process modelling and quality requirements and the goes on to discuss wafer forming and wafer surface preparation techniques. The whole is rounded off with a chapter on the research and future challenges in wafer manufacturing.

Sie lesen das E-Book in den Legimi-Apps auf:

Seitenzahl: 560

Veröffentlichungsjahr: 2021

Ähnliche

Table of Contents

Cover

Wafer Manufacturing

Copyright

Preface

Acknowledgement

Part I: From Crystal to Prime Wafers

1 Wafers and Semiconductors

1.1 Introduction

1.2 Semiconductor Revolution

1.3 Silicon Wafers Used in Device Manufacturing (IC and MEMS)

1.4 Surface Properties and Quality Measurements of Wafers

1.5 Other Properties and Quality Requirements of Silicon Wafers

1.6 Economics of Wafer Manufacturing

1.7 Summary

References

Notes

2 Wafer Manufacturing: Generalized Processes and Flow

2.1 Introduction

2.2 Wafer Manufacturing: Generalized Process Flow

2.3 Crystal Growth

2.4 Wafer Forming

2.5 Wafer Polishing

2.6 Wafer Preparation

2.7 Industrial Processes of Wafer Manufacturing

2.8 Summary

References

Notes

3 Process Modeling and Manufacturing Processes

3.1 Introduction

3.2 Wafer Manufacturing and Brittle Materials

3.3 Ductile Machining Versus Brittle Machining

3.4 Abrasive Machining in Wafer Manufacturing

3.5 Abrasive Materials

3.6 Ductile Machining of Brittle Materials

3.7 Process Modeling of Wafer Manufacturing Processes

3.8 Abrasive Slurry in FAM Processes

3.9 Summary

References

Notes

Part II: Wafer Forming

4 Wafer Slicing Using a Modern Slurry Wiresaw and Other Saws

4.1 Introduction

4.2 The Modern Wiresaw Technology

4.3 The Three Categories of Saw for Wafer Slicing

4.4 Inner‐diameter (ID) Saw

4.5 The Modern Slurry Wiresaw

4.6 Comparison Between the ID Saw and Wiresaw

4.7 Research Issues in Wiresaw Manufacturing Processes

4.8 Summary

References

Notes

5 Modeling of the Wiresaw Manufacturing Process and Material Characteristics

5.1 Introduction

5.2 The Rolling‐indenting Model

5.3 Vibration Modeling and Analysis

5.4 Damping Factor of the Slurry Wiresaw Systems

5.5 Elasto‐hydrodynamic Process Modeling

5.6 Thermal Management

5.7 Wire, Wire Web, and Slurry Management

5.8 Summary

References

Notes

6 Diamond‐Impregnated Wire Saws and the Sawing Process

6.1 Introduction

6.2 Manufacturing Processes of Diamond‐impregnated Wires

6.3 Slicing Mechanism of a Diamond Wire Saw

6.4 Properties of Wafers Sliced by Diamond Wire Saws

6.5 Slicing Performance with Different Process Parameters

6.6 Summary

References

Notes

Part III: Wafer Surface Preparation and Management

7 Lapping

7.1 Introduction

7.2 Fundamentals of Lapping and FAM

7.3 Various Configurations and Types of Lapping Operation

7.4 Lapping and Preliminary Planarization

7.5 Technical Challenges and Advances in Lapping

7.6 Summary

References

Notes

8 Chemical Mechanical Polishing

8.1 Introduction

8.2 Chemical Mechanical Polishing (CMP)

8.3 Polishing Pad Technology

8.4 Polishing Slurry Technology

8.5 Edge Polishing

8.6 Summary

References

Notes

9 Grinding, Edge Grinding, Etching, and Surface Cleaning

9.1 Introduction

9.2 Wafer Grinding for Surface Processing

9.3 Edge Grinding

9.4 Etching

9.5 Surface Cleaning

9.6 RCA Standard Clean

9.7 Summary

References

Notes

10 Wafer Metrology and Optical Techniques

10.1 Introduction

10.2 Evaluation and Inspection of the Wafer Surface

10.3 Wafer Defects and Inspection

10.4 Measurement of the Wafer Surface Using Moiré Optical Metrology

10.5 Summary

References

Notes

11 Conclusion

11.1 (I) From Crystal to Prime Wafers

11.2 (II) Wafer Forming

11.3 (III) Wafer Surface Preparation and Management

11.4 Final Remarks

Index

End User License Agreement

List of Tables

Chapter 1

Table 1.1 Resistivity of selected materials in

m, as defined in Equation (1....

Table 1.2 Wafer diameters and thickness.

Table 1.3 Convention of the orientation flats for wafers with diameters of 15...

Table 1.4 Results of example in Figure 1.7 with probe B shifted downward by f...

Table 1.5 Four‐character acronyms for wafer flatness measurement.

Table 1.6 A summary of various surface roughness measures.

Table 1.7 Material properties of the Young's modulus and Poisson's ratio of s...

Chapter 2

Table 2.1 Comparison between the two melt growth methods: CZ and FZ growth.

Chapter 3

Table 3.1 Some selected average particle sizes of abrasive materials, as defi...

Table 3.2 ANSI standard size for microgrits, based on B74.10.2010 [ANSI (2010...

Table 3.3 Knoop hardness and Mohs hardness of selected abrasive materials.

Table 3.4 Comparison between slicing using a slurry wiresaw and lapping in wa...

Chapter 4

Table 4.1 Comparisons between uni‐directional and bi‐directional wire motion ...

Table 4.2 Comparison of various properties between the modern slurry wiresaw ...

Chapter 5

Table 5.1 Wire size versus the critical speed and the fundamental natural fre...

Chapter 6

Table 6.1 Comparison of resinoid and electroplated diamond wires.

Table 6.2 Manufacturing conditions of a resinoid diamond wire.

Table 6.3 Comparison between operating properties of diamond wire saws and sl...

Table 6.4 Comparison of various common abrasive machining types in wafer manu...

Chapter 8

Table 8.1 Specifications for polished silicon wafers of 150, 200, and 300 mm.

Table 8.2 Specifications under the “lithography and patterning” requirement f...

Chapter 9

Table 9.1 The wafer edge profiles of 300 mm wafers, with value ranges of

,

,...

Table 9.2 The wafer edge profiles of 450 mm wafers, with value ranges of the ...

Table 9.3 RCA Standard Clean: mixture of the solution SC‐1

Table 9.4 RCA Standard Clean: mixture of the solution SC‐2

Chapter 10

Table 10.1 Comparison of capacitive versus shadow moiré methods

Table 10.2 Modulo

phase correction

List of Illustrations

Chapter 1

Figure 1.1 The first transistor, made of germanium, at the AT&T Bell Laborat...

Figure 1.2 Silicon with purity higher than 99.9%.

Figure 1.3 (Left) Convention of the orientation notch, indicating the primar...

Figure 1.4 Plot of CPU microprocessor transistor counts from 1971 to 2018 an...

Figure 1.5 Illustration of a wafer under non‐contact characterization of sur...

Figure 1.6 Illustration of the calculation of the warp of a wafer with respe...

Figure 1.7 Example illustrating the calculation of TTV, bow and warp of a wa...

Figure 1.8 Definition of the planar coordinate system of wafers: (a) on a wa...

Figure 1.9 Classification of topographical features based on their spatial w...

Figure 1.10 Illustration of a surface profile and roughness with the termino...

Figure 1.11 Illustration of the mean roughness height

, or the average maxi...

Figure 1.12 Illustration of the ten‐point roughness height

(ISO), or the te...

Figure 1.13 3D illustration for a DOA in (100) crystal. The illustrated DOA ...

Figure 1.14 (a) Variation of DOA with respect to the [010] on (100) crystal....

Figure 1.15 (a) Variation of DOA with respect to the [001] direction on (110...

Figure 1.16 Plot of gravity‐induced deflection of a 300 mm wafer due to its ...

Figure 1.17 Plot of gravity‐induced deflection of a 300 mm wafer due to its ...

Figure 1.18 Photos of a lithium niobate wafer (left), and a silicon prime wa...

Figure 1.19 Photos of polycrystalline silicon PV wafers with rectangular and...

Figure 1.20 Photos of a thin piece of aluminum sliced by a wiresaw (left), a...

Chapter 2

Figure 2.1 Process flow and the four categories of wafer manufacturing proce...

Figure 2.2 An illustration of the Czochralski (CZ) crystal growth

Figure 2.3 A single crystalline silicon ingot produced by CZ bulk growth, sh...

Figure 2.4 A plot of maximum theoretical pulling speeds of silicon in CZ bul...

Figure 2.5 Float‐zone (FZ) growth.

Figure 2.6 Schematic of Bridgman growth, in a horizontal configuration. The ...

Figure 2.7 Schematic of Bridgman–Stockbarger growth in a vertical configurat...

Figure 2.8 Epitaxial growth on a wafer substrate depicting the interface at ...

Figure 2.9 Illustration of epitaxial growth on a wafer.

Figure 2.10 Four approaches of crystal growth, along with reference to the s...

Figure 2.11 Schematic of an inner‐diameter (ID) saw for wafer slicing.

Figure 2.12 Schematic of a modern wiresaw for the slicing of a polycrystalli...

Figure 2.13 Photo of a single‐pass, reciprocating saw using a wire impregnat...

Figure 2.14 (a) Left: CZ crystal growth equipment and a view window. Right: ...

Figure 2.15 A real‐time CCD camera image acquired during a CZ crystal growth...

Figure 2.16 Left: lowering a silicon boule from the growth chamber. Center: ...

Figure 2.17 Boule/ingot is sliced into segments of manageable length for waf...

Figure 2.18 Left: silicon ingot before trimming using surface grinding. Righ...

Figure 2.19 X‐ray diffraction equipment for the measurement of crystalline o...

Figure 2.20 Wafer forming. Left: An industrial slurry wiresaw for slicing an...

Figure 2.21 Wafer polishing. Left: a lapping machine that processes multiple...

Figure 2.22 Post‐lapping to pre‐polishing equipment and processes: (a) acid ...

Figure 2.23 Illustration of the negative impacts on lithography with particl...

Figure 2.24 Wafer polishing equipment: Polishing of wafers, with a zoom‐in v...

Figure 2.25 Wafer preparation. Left: pre‐cleaning after the polishing proces...

Figure 2.26 Wafer preparation. Left: appearance inspection. Center: particle...

Chapter 3

Figure 3.1 Typical stress–strain curves for brittle and ductile materials. B...

Figure 3.2 (a) Ductile machining: high‐speed photo of ductile machining with...

Figure 3.3 (a) An illustration of the bonded abrasive machining (BAM) proces...

Figure 3.4 Schematic of the “three‐body‐abrasion” process showing the cuttin...

Figure 3.5 FEM photos of silicon carbide abrasives: (a) FEPA F400 silicon ca...

Figure 3.6 Schematic for various processes in FAM. The cutting tool can be a...

Figure 3.7 (a) A photo of the surface of a silicon wafer with an abrasive gr...

Figure 3.8 Long scratches resulting from the lapping experiment with

m mean...

Figure 3.9 Models of the two mechanisms of FAM processes: rolling‐indenting ...

Figure 3.10 Experimental results on the relationship of the viscosity and sh...

Figure 3.11 Experimental results on the effect of slurry water content on th...

Figure 3.12 SEM photos of (a) fresh SiC abrasive grits (F‐400 grits), and (b...

Chapter 4

Figure 4.1 A photo of a wire for quarrying in 1901, a new method of slate mi...

Figure 4.2 (a) A schematic of the wire saw for quarrying in 1901 (free abras...

Figure 4.3 (a) Schematic of a conventional ID saw for wafer slicing; (b) the...

Figure 4.4 SEM photos of the surface sliced by an ID saw: (left) photo with ...

Figure 4.5 A photo of a dressing stick made of green silicon carbide, used i...

Figure 4.6 Photo of a modern industrial wiresaw for wafer slicing.

Figure 4.7 Schematic of a wiresaw and illustration of wire management and te...

Figure 4.8 A schematic illustration of an ingot on a wire web formed by the ...

Figure 4.9 Wire web spun with a configuration of (a) two‐wire guide cylinder...

Figure 4.10 An ingot glued to a ceramic fixture base using an epoxy glue....

Figure 4.11 An illustration of the thickness of a wafer, as related to the w...

Figure 4.12 An illustration showing two ingots been fed unto the wire web su...

Figure 4.13 Illustration of a wire entering a ingot, forming a bow angle wit...

Figure 4.14 Different configurations of feeding an ingot onto the wire web f...

Figure 4.15 Schematic diagrams and comparison of (a) the modern wiresaw, and...

Chapter 5

Figure 5.1 Horizontal and parallel tool marks made by the wire of a wiresaw ...

Figure 5.2 Typical surface of an as‐sliced silicon wafer made by modern slur...

Figure 5.3 The engineering model of the slurry wiresaw manufacturing process...

Figure 5.4 Illustration of the “rolling‐indenting” and “scratching‐indenting...

Figure 5.5 A schematic showing the wire and process parameters of a wire mov...

Figure 5.6 Three‐dimensional plots of the normalized vibration amplitude und...

Figure 5.7 Three‐dimensional surface plots of the critical speed of a moving...

Figure 5.8 Left: Three‐dimensional plot of the forced vibration analysis und...

Figure 5.9 Left: Magnitudes of the frequency response with respect to differ...

Figure 5.10 Free vibration response with with initial displacement

and dif...

Figure 5.11 Elasto‐hydrodynamic pressure profile in the cutting zone for 100...

Figure 5.12 Profile for the film thickness in the cutting zone for a 100 mm ...

Figure 5.13 (a) Surface of an as‐sliced silicon wafer by the wiresaw shows a...

Figure 5.14 Optical arrangement for real‐time monitoring of wire diameter du...

Figure 5.15 Illustration of a wire in a groove on the surface of wire guide ...

Figure 5.16 Moiré fringes created by two superimposed gratings for the detec...

Figure 5.17 Moiré fringes generated by distortion of wire alignment in a wir...

Chapter 6

Figure 6.1 A steel wire with beads impregnated by diamond abrasive grits, mo...

Figure 6.2 SEM images of a diamond wire showing (a) a view of the wire's cir...

Figure 6.3 Illustration of the manufacturing apparatus of resinoid diamond w...

Figure 6.4 Illustration of the manufacturing apparatus of electroplated diam...

Figure 6.5 SEM images of surfaces of silicon wafers, in the same scale of 10...

Figure 6.6 Illustration of the diamond wire moving direction and the formati...

Figure 6.7 Cross‐sectional TEM images of surface of a silicon wafer sliced b...

Chapter 7

Figure 7.1 Processes of “wafer polishing” which includes lapping, etching, a...

Figure 7.2 Surface of a silicon wafer after a lapping operation with larger ...

Figure 7.3 Logitech PM5 lapping equipment for conducting lapping research at...

Figure 7.4 A schematic of a single‐sided lapping machine.

Figure 7.5 A schematic of an industrial double‐sided lapping machine with fi...

Figure 7.6 Schematic to illustrate the processes of “wafer grinding” followe...

Chapter 8

Figure 8.1 Schematic of chemical mechanical polishing (CMP) equipment: (a) a...

Figure 8.2 Schematic of CMP equipment: (a) a photo of CMP equipment with waf...

Chapter 9

Figure 9.1 Schematic of a wafer on a wafer holder and a diamond grinding whe...

Figure 9.2 Schematic of the wafer edge profiles and its relevant characteris...

Chapter 10

Figure 10.1 Surface measurement of a 150 mm silicon wafer sliced by a slurry...

Figure 10.2 The moiré fringes resulting from rotation between two identical ...

Figure 10.3 Optical arrangement of the shadow moiré method: a laser incident...

Figure 10.4 A photo with moiré fringes for the surface of a single crystalli...

Figure 10.5 Measurement of a polished calibration specimen: four shifted ima...

Figure 10.6 The phase pattern of the calibration measurement, visualizing th...

Figure 10.7 Surface topology of the calibration specimen, without compensati...

Figure 10.8 Surface topology of the calibration specimen after the orientati...

Figure 10.9 The four shifted images of a regular wafer surface from (a) to (...

Figure 10.10 The phase pattern, visualizing the phase distribution on the wa...

Figure 10.11 Wafer surface topology of an as‐sliced wafer shown in Figure 10...

Figure 10.12 Surface topology of a wiresawed wafer after flattening the

an...

Figure 10.13 Surface topology of an as‐sliced wafer after compensating for t...

Guide

Cover Page

Title Page

Copyright

Preface

Acknowledgement

Table of Contents

Begin Reading

Index

WILEY END USER LICENSE AGREEMENT

Pages

iv

xi

xii

xiii

xiv

1

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

189

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

209

210

211

212

213

214

215

216

217

218

219

220

221

223

224

225

226

227

228

229

230

231

232

233

234

235

236

237

238

239

240

241

242

243

244

245

246

247

248

249

250

251

252

253

254

255

256

257

258

259

260

261

262

263

264

265

266

267

268

269

270

271

272

273

274

275

276

277

279

280

281

282

283

284

285

286

287

288

289

290

291

Wafer Manufacturing

Shaping of Single Crystal Silicon Wafers

Imin I. Kao

SUNY at Stony Brook UniversityUSA

Chunhui Chung

National Cheng Kung UniversityTaiwan

This edition first published 2021

© 2021 John Wiley & Sons Ltd

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, except as permitted by law. Advice on how to obtain permission to reuse material from this title is available at http://www.wiley.com/go/permissions.

The right of Imin Kao and Chunhui Chung to be identified as the authors of this work has been asserted in accordance with law.

Registered Offices

John Wiley & Sons, Inc., 111 River Street, Hoboken, NJ 07030, USA

John Wiley & Sons Ltd, The Atrium, Southern Gate, Chichester, West Sussex, PO19 8SQ, UK

Editorial Office

The Atrium, Southern Gate, Chichester, West Sussex, PO19 8SQ, UK

For details of our global editorial offices, customer services, and more information about Wiley products visit us at www.wiley.com.

Wiley also publishes its books in a variety of electronic formats and by print‐on‐demand. Some content that appears in standard print versions of this book may not be available in other formats.

Limit of Liability/Disclaimer of Warranty

In view of ongoing research, equipment modifications, changes in governmental regulations, and the constant flow of information relating to the use of experimental reagents, equipment, and devices, the reader is urged to review and evaluate the information provided in the package insert or instructions for each chemical, piece of equipment, reagent, or device for, among other things, any changes in the instructions or indication of usage and for added warnings and precautions. While the publisher and authors have used their best efforts in preparing this work, they make no representations or warranties with respect to the accuracy or completeness of the contents of this work and specifically disclaim all warranties, including without limitation any implied warranties of merchantability or fitness for a particular purpose. No warranty may be created or extended by sales representatives, written sales materials or promotional statements for this work. The fact that an organization, website, or product is referred to in this work as a citation and/or potential source of further information does not mean that the publisher and authors endorse the information or services the organization, website, or product may provide or recommendations it may make. This work is sold with the understanding that the publisher is not engaged in rendering professional services. The advice and strategies contained herein may not be suitable for your situation. You should consult with a specialist where appropriate. Further, readers should be aware that websites listed in this work may have changed or disappeared between when this work was written and when it is read. Neither the publisher nor authors shall be liable for any loss of profit or any other commercial damages, including but not limited to special, incidental, consequential, or other damages.

Library of Congress Cataloging‐in‐Publication Data

Names: Kao, Imin, author. | Chung, Chunhui, author.

Title: Wafer manufacturing : shaping of single crystal silicon wafers /

Imin Kao, Chunhui Chung.

Description: First edition. | Hoboken, NJ : Wiley, 2021. | Includes

bibliographical references and index.

Identifiers: LCCN 2020034639 (print) | LCCN 2020034640 (ebook) | ISBN

9780470061213 (hardback) | ISBN 9781118696255 (adobe pdf) | ISBN

9781118696231 (epub) | ISBN 9781118696224 (obook)

Subjects: LCSH: Semiconductor wafers–Design and construction.

Classification: LCC TK7871.85 .K295 2021 (print) | LCC TK7871.85 (ebook)

| DDC 621.3815/2–dc23

LC record available at https://lccn.loc.gov/2020034639

LC ebook record available at https://lccn.loc.gov/2020034640

Cover Design: Wiley

Cover Image: © kynny / Getty Images

Preface

This book is designed and written with both research and engineering practice in mind. Subjects pertaining to the fundamentals of wafer manufacturing and recent research advances are presented, as well as practical engineering and technology for practitioners in this industry. This book is ideal for a novice who wants to gain insightful information and knowledge about wafer manufacturing, and to learn how the prime (or premium) wafers that are used in microelectronics fabrication are produced. At the same time, this book is full of research topics and presentations of advances in fundamental knowledge about relevant manufacturing processes such that it will meet the needs of curious minds who want to investigate issues beyond the status quo and to study these processes with an objective to improve a myriad of related manufacturing processes.

Wafer manufacturing has been a field in which experience and engineering know‐how has played a significant role and was of instrumental value to the industry. With the emergence of new technology and research, the challenges are to understand fundamental process modeling in various manufacturing processes of wafer manufacturing, and to be able to apply this new knowledge in the process control and management of wafering processes. With the familiarity of both research issues and practical engineering, the authors strive to achieve the goals stated above.

The book is a must‐have for engineers and researchers in the field of wafer production and manufacturing. Although single crystalline silicon wafers are the majority of wafering done today in the industry, this book is also equally applicable, in many regards, to the wafer production of various crystal ingots such as III–V and II–VI compounds, silicon carbide, lithium niobates, and others.

It has been a major undertaking to commit to writing a book like this, although I have been conducting research in wafer manufacturing since 1994. This project has taken more time than was estimated initially when the first agreement was signed with the Wiley publisher. My goal was and still is to make this book a resource for those who want to understand the many aspects of wafer manufacturing technologies, as well as for those practitioners who want to utilize the knowledge to improve the existing processes.

Strict quality control has been imposed on the content of this book and subjects have been added or removed along the process of writing to make it as relevant as possible, based on the best judgment in the field. This book is put together with the best intent and effort, although it is far from being perfect. I welcome feedback and comments from readers, who can email me at [email protected], or send postal mail to: Professor Imin Kao, Department of Mechanical Engineering, Stony Brook, NY 11794‐2300, USA.

Acknowledgement

This book is a culmination of many years of research on the subject, and has had the help of many colleagues, students, and mentors along the path of my academic career. Dr. Tai‐ran Hsu, who gave me an opportunity as an assistant professor at San Jose State University, is a mentor and an inspiration when he endeavored to conduct research and study in MEMS in 1991, with the outcome of a book in MEMS (McGraw‐Hill 2002). My research at Stony Brook University (SBU, State University of New York, SUNY) on the topic of wafer manufacturing started in 1994 when I joined SBU. I started this research with a grant from the DoE and collaborated with Dr Vish Prasad on innovative growth techniques of photovoltaic wafers, and slicing using a slurry wiresaw, which was a new machine tool for slicing ingots to wafers at that time. The research continued to be funded by NSF and industrial grants. The collaboration with Dr Fu‐pen Chiang, who is a reputed and renowned researcher in optical metrology, led to work in novel wafer surface measurements and real‐time monitoring of wire wear and wire web using optical metrology. Many PhD and MS students of mine worked on pioneering modeling and research on slurry wiresaws and wafer manufacturing that led to some of the contents of this book. I am grateful to have the dedication and contributions of Drs Milind Bhagavat (who started the concept of this book with me), Liqun Zhu, Songbin Wei, Sumeet Bhagavat, Chunhui Chung (who is a coauthor of this book), and Liming Li.

In addition, I would like to thank Professor Chao‐Chang Arthur Chen of the National Taiwan University of Science and Technology and the Global Wafer Co., Limited in Taiwan that provided images of wafer manufacturing processes for my book. The images are used to illustrate various wafer manufacturing processes, from crystal growth to polished prime wafers, and make for a better presentation and relevance of the manufacturing processes.

I was fortunate to be working with some of the best colleagues at SBU when I was asked to step into various roles in administration, and participated in the establishment of innovative education initiatives, such as the Undergraduate Colleges system, new departments, and SUNY Korea – a global campus of SBU at Incheon, Korea. My mentor, Dr Yacov Shamash, helped me to appreciate the rigours in academic administration. I took a six‐month sabbatical leave in 2016 at SUNY Korea to carry out my role as the Executive Director of SUNY Korea Academic Programs, and to spend more time on writing this book. I am very appreciative of the then President ChoonHo Kim with whom I partnered and participated in the daunting work, with a broader team at SBU and in Korea, in establishing a global university in a new mold with an academia–government–industry trilateral collaboration at an international level. Juggling administrative tasks with my research has been an intriguing challenge for me over the years, nonetheless.

Most importantly, I am forever grateful to my wife and life‐long partner, Elaine Chang, who has been a stalwart supporter for me over more than 37 years of marriage. Without her unwavering support and considerable influence, this book would not have been possible. We have three children, Drs Katherine Kao, Jonathan Kao, and Emmeline Kao, who have helped with reading this work and have commented on it. I am indeed blessed to have my family and God in my life.

February 2020

Imin Kao

at Stony Brook, New York

Part IFrom Crystal to Prime Wafers

1Wafers and Semiconductors

1.1 Introduction

The fundamental building block from which microelectronic integrated circuit (IC) chips, MEMS (micro electro mechanical systems) devices, and microelectronic devices and systems are constructed is called a “wafer.” This book discusses the nuances of the wafer manufacturing (or wafer production) technology and process, as well as the recent research and development contributing to the growth of the technologies in wafer manufacturing. Each chapter has a References section at the end to provide a list of books and articles for reference and further reading or study on the subjects presented.

This chapter provides basic information about wafers and the semiconductor revolution that has influenced our modern daily lives, including the subjects of silicon, wafers, mechanical materials, and surface properties.

1.2 Semiconductor Revolution

1.2.1 Classification of Materials

Materials are classified, based on their electrical conductivity, into the following four categories: conductor, insulator, superconductor, and semiconductor. Table 1.1 lists a few selected materials in the three most common categories and their resistivity values in m. The resistance of a material, is defined as follows

where is the resistivity and and are the length and cross‐sectional area of the material, respectively. When a voltage is applied to a material, it may cause electrical current to flow, depending on the resistivity of the material. The electrical resistivity is thus defined as the ratio between the electric field and the density of the current it creates, as in the following equation

where is the electric field applied inside the material with a unit of V , and is the current density in A m, also measured inside the material. The conductivity is the inverse of resistivity as follows

Four classifications of material are described in the following.

Conductor – these materials conduct current when a voltage is applied. Examples include metals, many metal alloys, and carbon. Metals are the best naturally occurring conductors of electricity, because of their metallic bonding, and thus have low resistivity (see

Table 1.1

).

Insulator – these materials conduct no current when a voltage is applied. Nevertheless, the current will suddenly pass through the material if the voltage is high enough, for example, in the form of an arc or plasma. An insulator is sometimes referred to as a dielectric, which describes non‐conduction of a direct current. The dielectric strength of an insulating material, then, is the electrical potential required to break down the insulator per unit thickness, with typical unit in V

(or V

). Examples of insulator materials include silicon dioxide (

), glass, ceramic materials, polymers, etc. Most ceramics and polymers, whose electrons are tightly bound by covalent and/or ionic bonding, are typically poor conductors. Many of these materials are used as insulators because they possess high resistivity values (See

Table 1.1

).

Superconductor – a superconductor is a material that exhibits zero resistivity. Superconductivity is a phenomenon that is observed in certain materials at low temperatures near absolute zero at which zero electrical resistance and expulsion of magnetic fields take place in certain materials. Such materials hold great interest and promise for many applications such as power transmission, magnetic levitation, and electronic switching.

Semiconductor – a semiconductor is dielectric in its natural state, but can conduct electricity under some conditions, either due to the addition of an impurity or because of temperature effects, but not others. Such characteristics make semiconductor materials a good medium for the control of electrical current. The resistivity of a semiconductor lies between that of insulators and conductors. Typical resistivities of semiconductor materials range from 10 to

m. Semiconductors are the foundation of modern electronics, including computers, electronic devices, and smart phones. Semiconductor solar photovoltaic panels directly convert light energy into electricity.

Table 1.1 Resistivity of selected materials in m, as defined in Equation (1.1). Superconductors have zero resistivity.

Values of resistivity vary depending on condition and environment, such as impurity and temperature. The commonly used unit in semiconductors is cm, with 1 m = 100 cm.

Conductors

Resistivity

Insulators

Resistivity

Semiconductors

Resistivity

Aluminum

Polyurethane

Silicon

Silver

Rubber

–

Germanium

Copper

–

GaAs

–

Carbon

Glass

–

SiC

–

Common semiconducting materials are crystalline solids. Silicon is the most popular commercial semiconductor material. Many other materials are used, including germanium, gallium arsenide (GaAs), indium phosphide (InP), and silicon carbide (SiC). The electronic properties and the conductivity of a semiconductor can be changed by “doping,” referring to a diffusion process that adds other materials to the semiconductor materials. This is typically achieved during crystalline silicon growth by adding boron or phosphorus impurities to the melt and then allowing it to solidify into silicon during the crystal growth process.

1.2.2 Semiconductor Revolution Today

Presently we are in the midst of a “semiconductor revolution.” Many objects with which we are associated today have either semiconductor devices built in or have been manufactured with a machine that contains in‐built semiconductor devices. These modern times are the “semiconductor era”, akin to the “steel era” that propelled the “second industrial revolution” in the 19th century. In the last several decades, semiconductor technology has grow in leaps and bounds, partly driven by consumerism generated by telecommunication, wireless internet, and information technology and partly by the need for automation catering to mass or batch production and manufacturing of technologically sophisticated products. Thanks to semiconductor technology, we are now able to manufacture very complex products in large quantities at lower costs.

Today's world is embraced by three technologies, each in a different stage of maturity:

The microelectronics technology with integrated circuits (ICs) has been at the forefront of all the breath‐taking achievements realized in the past few decades. At the core of IC technology is the development of very tiny but extremely robust electrical circuits that can act as the brain of a machine, such as that in a controller, computer, or smart devices. The road of microelectronics technology was paved with the invention of the first transistor in 1947 [American Physical Society (

2000

); Riordan and Hoddeson (

1997

)], as shown in

Figure 1.1

. The batch fabrication of transistors using planar technology enables the IC technology we know today. IC technology has been growing rapidly since the 1970s and since that time it has never shown any sign of decline. Radically new technologies and new products are still being introduced into the market every year and new concepts and innovations are being researched that will keep this technology moving for years to come.

The fabrication technology of IC has given birth to the world of MEMS (micro electro mechanical systems) which integrates the electrical power of ICs with micron‐scale mechanical structures to build powerful applications pertaining to the real world. An example is air‐bag sensors in automobiles. MEMS technology is in an exciting phase; it has already been utilized in everyday applications and is still concurrently looking for new applications. The “satellite navigation” industry and the “computer gaming industry” have already presented some new avenues, and there are undoubtedly many more opportunities to realize.

Figure 1.1 The first transistor, made of germanium, at the AT&T Bell Laboratory.

(Source: AT&T)

On the horizon is the new enticing world of “nanotechnology”, which encompasses both fundamental research and promising applications in fields such as medicine, energy, biomedical, etc. At the root of nanotechnology is the confluence of electrical, mechanical, chemical, physical, and biological sciences and engineering. The fields of nanotechnology hold a lot of future promise.

The most fundamental part of the semiconductor world is the “semiconductor material” used to realize the technologies. In layman's parlance, semiconductors can show electrical conductivity between conductors and insulators, as described in Section 1.2.1. This property by itself is not enough to realize the technologies (ICs and MEMS) we know of today. What really drives today's semiconductor world are the properties of some of the semiconductors that allow their conductivity to be manipulated by either electrical signals or by processing. This is the property that enables the working of “transistors” which are the fundamental building blocks of semiconductor devices. Some semiconductor materials that have found their way into device applications are silicon, germanium, silicon carbide, gallium arsenide, indium phosphide, lithium niobate, and many more. By far, silicon is the most popular semiconductor material. Silicon meets more than 95% of the world's semiconductor needs.

1.2.3 Silicon Wafers and Solar Cells

Silicon as a semiconductor material has also found application in solar cells. As the world is facing the prospect of depletion of conventional energy sources, more emphasis is being put on harnessing unconventional energy such as solar energy. Silicon is the backbone of “solar cell” technology. Many of the demands that are put on silicon wafers in semiconductors are also applicable to the solar world. The only place where the solar world diverges from semiconductors is that semiconductor applications need single‐crystalline (or mono‐crystal) materials, while the solar cells can use single‐ or quasi‐single‐ or poly‐crystalline materials. Still, there is a lot of similarity between the manufacturing of wafers for IC chips and for solar cells. The mechanical properties needed for a semiconductor wafer or solar wafer are more or less similar. This book also discusses the wafer manufacturing issues associated with the solar industry.

1.3 Silicon Wafers Used in Device Manufacturing (IC and MEMS)

Silicon is a blue‐gray, brittle chemical element in the same group as carbon and germanium in the periodic table and shares similar properties to microelectronic materials. Figure 1.2 shows pieces of high‐purity, ready to melt silicon for growing boules. Comprising 28% of the earth's elements, silicon is second only to oxygen as the most common element on the surface of the earth. Silicon is a key ingredient in glasses, quartz, soil, and sand. As a brittle material, silicon has hardness and structural strength comparable to many metals such as aluminum and bronze. Semiconductor devices, or chips, are fabricated on a silicon substrate in the form of a wafer. The manufacture of silicon wafers begins with the growth of a single‐crystalline silicon ingot (or boule). A single‐crystalline silicon crystal is a boule composed of atoms arranged in a three‐dimensional periodic pattern that extends throughout the material, required for semiconductor fabrication. Polycrystalline silicon crystals are formed with random orientations, and are therefore cheaper to manufacture. They are often used in photovoltaic solar devices.

Figure 1.2 Silicon with purity higher than 99.9%.

Source: Imin Kao.

1.3.1 Standard Wafer Diameters and Sizes

Silicon wafers are available in a variety of diametral sizes from 25.4 mm (1 in) to 300 mm (12 in) [Gise and Blanchard (1986)], and the future wafer size of 450 mm (18 in). Semiconductor fabrication plants (also known as fabs) are defined by the size of wafers that they are tooled to produce. Silicon wafers have historically consisted of diameters/sizes shown in Table 1.2. The size has gradually increased to improve throughput and reduce cost with current state‐of‐the‐art semiconductor fabrication plants (fabs) processing wafers with a diameter of 300 mm (or 12 in). The next standard wafer size, as promoted by Intel, Samsung, TSMC, and SEMATECH, will be 450 mm (18 in) [SEMI (2012a); Young (2011a); Capraro (2013); Intel News Release (2008); Watanabe and Kramer (2006)]. This “industry transition to 450 mm wafers for leading‐edge chip manufacturing will be one of the most complex and costly decisions in the history of semiconductors” [SEMI (2012b)]. According to SEMATECH and SEMI, the “450 Consortia,” a consortium of researchers in semiconductor technology, has been effective at creating a level platform for consensus building to leverage experience and expertise of a larger community, including program scopes in equipment, materials, guidelines, and testing [Young (2011b)]. In recent years, the Global 450 Consortium (G450C) has been established as a 450 mm wafer and equipment development program that is leveraging industry and government investments to demonstrate 450 mm process capabilities at the Albany NanoTech Complex of the Colleges of Nanoscale Science and Engineering (CNSE) of SUNY Polytechnic Institute (SUNY Poly) [CNSE (2012); CNSE (2015)].

Table 1.2 Wafer diameters and thickness.

The largest current standard size of wafers is mm, with the next size of mm expected in the near future. The unit of m represents micrometer, or micron, with m mm m.

Wafer diameter in SI units

Equivalent wafer size

Typical wafer thickness

mm

1 inch

–

mm

2 inch

m

mm

3 inch

m

mm

4 inch

m

mm

4.9 inch

m

mm

5 inch

m

mm

6 inch

m

mm

8 inch

m

mm

12 inch

m

mm

18 inch

m

The 450 mm wafer is not simply an extension of the current technology for the 300 mm wafer. Reducing the defects of a 450 mm wafer is just as critical as discovering numerous technological breakthroughs and innovations.

Four factors are often mentioned in regard to improving the productivity of semiconductor manufacturing. They are

Increasing capital equipment utilization

Improving die yield

Enlarging wafer sizes

Shrinking device feature sizes.

While the device feature sizes continue to decrease, a SEMATECH study by Anderson (1997) indicates that the size of wafers in microelectronics fabrication has remained unchanged for approximately 24 years, allowing a return on investment (ROI) of R&D and capital investment of the equipment and technology. Nevertheless, the semiconductor industry needs to increase wafer sizes because of the overall cost reduction resulting from a larger percentage of usable real estate of wafer surface and more dice1 per wafer. The overall cost of manufacturing is reduced by using a larger wafer surface because more dice are produced using the same number of fabrication process steps. In addition, wafer size increases are also viewed in terms of the increase in wafer area. For example, the total surface area of a 300 mm (12 inch) wafer is 2.25 times larger than that of a 200 mm (8 inch) wafer, with an increase of 125% surface area. Likewise, the same increase of the wafer surface area is realized from 300 mm to 450 mm wafers.

1.3.2 Crystalline Orientation of Silicon Wafers

Table 1.3 illustrates the convention of wafer flats to indicate the crystallographic planes and doping for wafers with diameters 150 mm and smaller. The primary flat has the longest straight length along the circumference of the wafer, as shown at the bottom flats in the figure. The horizontal flats at the bottom of each wafer illustration indicate the major direction [1 1 0] along the primary flats. The secondary flat, if it exists, is the shorter straight length along the circumference of the wafer.

Modern wafers with a diameter of 200 mm or more use a notch to represent the crystallographic information with no visual indication of the doping type. Such a wafer with a notch is illustrated in Figure 1.3. The notch indicates the major direction [1 1 0] of the wafer, similar to the direction indicated by the primary flat in smaller wafers.

Wafers made of materials other than silicon may have different sizes and thicknesses as compared to the electronic silicon wafer. Wafer thickness is determined by the mechanical properties of the material, especially in bending with loading and deflection due to its own weight, so as not to crack or break during processing and handling in microelectronics fabrication. More details will be discussed in Section 1.5.3.

Table 1.3 Convention of the orientation flats for wafers with diameters of 150 mm or smaller. The longer side at the bottom is the “primary” flat; the shorter side is the “secondary” flat.

The Miller index is used here to denote plane with (…), and direction with […].

Wafer

‐type

‐type

(1 0 0)

(1 1 1)

Figure 1.3 (Left) Convention of the orientation notch, indicating the primary orientation of [1 1 0] for wafers with a diameter of 200 mm or larger. (Right) A photo of an as‐sliced silicon wafer of diameter 300 mm (12 in), with the orientation notch at the left side of the wafer.

Source: Imin Kao.

1.3.3 Moore's Law

Moore's Law (as it is commonly referred to) is an empirical observation and prediction of the scale and the number of transistors on chips or integrated circuits, which roughly doubles every two years [Moore (1965)]. This prediction has proven to be accurate for nearly five decades, partly because it has been used in the semiconductor industry to guide long‐term planning and to establish milestones for research and development. For example, an Intel website recently stated that “for decades, Intel has met this formidable challenge through investments in technology and manufacturing resulting in the unparalleled silicon expertise that has made Moore's Law a reality.” [Intel Corp. (2005)]. A plot of CPU microprocessor transistor counts from 1971 to 2018 is shown in Figure 1.4. Note the vertical axis is in logarithmic scale. The line in Figure 1.4 corresponds to a growth that doubles every two years, as predicted by Moore's law.

Although Moore's law was initially a prediction of the growth of the scale of transistors in microprocessors, this principle has been employed in various technologies and industries, typically as a measure in digital technology for the rate of growth in size, density, speed, capacity, etc., based on this binary power law.

1.4 Surface Properties and Quality Measurements of Wafers

The processes and quality of wafer manufacturing (especially semiconductor wafers) have been improved over the last decades in response to the innovative pace and rigorous requirements of the surface finish of semiconductor and solar industries. Several important properties of wafer surface properties and quality measurements will be discussed in the following sections.

Conventionally, wafer surfaces are measured and characterized by the parameters of total thickness variation (TTV), warp, bow, flatness, and waviness. Typically, the unit of TTV, warp, and bow is microns. As the wafer diameters become larger, the requirements of surface finish become more stringent and it remains important to maintain high yield in electronic fabrication. A few important surface properties are discussed in the following subsections.

1.4.1 Surface Waviness: TTV, Bow, and Warp

The bulk properties that characterize the surface of wafers are best illustrated by Figure 1.5 in which a wafer spins between two capacitive probes that sample points on the wafer surfaces. Different surface measures are defined as presented in the following, based on various ASTM standards: for TTV in [ASTM Standard F1390 (2002); ASTM Standard F533 (2002); ASTM Standard F657 (1999)], for bow in [ASTM Standard F534 (2002)], and for warp in [ASTM Standard F1390 (2002); ASTM Standard F657 (1999)]. These ASTM standards had been withdrawn in May 2003, and were transferred to SEMI (www.semi.org). The SEMI documents describing the TTV, bow and warp can be found in [SEMI 3D12 (2015); SEMI MF1390 (2018); SEMI MF1530 (2018); SEMI MF533 (2010); SEMI MF534 (2014); SEMI MF657 (2014)].

Figure 1.4 Plot of CPU microprocessor transistor counts from 1971 to 2018 and Moore's Law.

Source: Moore's Law – The number of transistor on integrated circuit chips (1971–2018). Retrieved from: https://ourworldindata.org/uploads/2019/05/Transistor-Count-over-time-to-2018.png. Licensed under CCBY SA.

Figure 1.5 Illustration of a wafer under non‐contact characterization of surface measurement. The probes A and B are typically a pair of capacitive probes that detect the distances and in automated non‐contact scanning.

The terminologies of TTV, bow, and warp, used to define wafer surface properties, are often referred to when describing the quality of surface finish of wafers. The following terms are first defined for the description of the various surfaces of a wafer.

Front surface

– the exposed surface upon which active semiconductor devices have been or will be fabricated.

Back surface

– the exposed surface opposite to that upon which active semiconductor devices have been or will be fabricated.

Median surface

– the locus of points in the wafer equidistant between the front and back surfaces, as shown in

Figure 1.5

.

Figure 1.5 shows a wafer, spinning along its centroidal axis as it passes through the gap between a pair of non‐contact probes A and B, typically capacitive sensors. The distances and are measured by the probe sensors, with the gap distance calibrated. As a result, the thickness of the wafer, , at the time of the sampling and measurement as the wafer surface passes through the gap between the probes is

Based on the schematic of measurement in Figure 1.5 and Equation (1.4), the following bulk properties are presented.

Among the sampled points on the wafer after completion of the spin and scan, the total thickness variation (TTV) is calculated as the difference between the maximum and minimum values of the thickness of the wafer, as follows

Further reference of TTV can be found in [ASTM Standard F1530 (2002); ASTM Standard F533 (2002); SEMI MF1530 (2018); SEMI MF533 (2010); SEMI MF657 (2014)].

Bow is the deviation of the center point of the median surface of a free, unclamped wafer from a median‐surface reference plane established by three points equally spaced on a circle with diameter a specified amount less than the nominal diameter of the wafer [ASTM Standard F534 (2002); SEMI MF534 (2014); SEMI MF1390 (2018)]. Referring to Figure 1.5 with the definition of the distance from the reference plane at the midspan between the probes A and B, we have

Consequently, the bow of the wafer, , can be derived from both equations above as

Bow is a measure of the concave or convex deformation of a wafer, based on the center of the wafer, independent of any thickness variation. Positive values of bow denote a convex (dome‐shaped) median surface when the wafer is positioned with its front surface up. Conversely, negative values of bow denote a concave (bowl‐shaped) median surface.

Warp is the difference between the maximum and the minimum distances of the median surface of a free, unclamped wafer from the reference plane [ASTM Standard F1390 (2002); ASTM Standard F657 (1999); SEMI MF1390 (2018); SEMI MF657 (2014)]. Like bow, warp is the measurement of the difference of the median surface with respect to a reference plane. Unlike bow, which measures only the difference at the center point of a wafer, warp uses the entire median surface of the wafer to determine the difference between the maximum and minimum distances, taking into consideration the signs of such distances. This is illustrated in Figure 1.6, in which a reference plane is established, as shown, and the maximum and minimum distances of the median surface of the wafer from the reference plane are labeled as and , respectively. Thus, warp is obtained as

Note that the signs of the distances are included to determine the optimal values, and to obtain the warp. When the reference plane is at the midspan between probes A and B, as in Figure 1.5, the distance is the same as ; thus, the warp can be deduced as follows

Figure 1.6 Illustration of the calculation of the warp of a wafer with respect to a reference plane. The distance is measured from the reference plane. In the case when the reference plane is at the midspan between the two probes A and B, as in Figure 1.5, the distance is the same as .

Note that the warp defined in Equation (1.8), with the reference plane defined as the midspan between the two probes A and B, is only a function of the measurements and . However, the warp is dependent upon the location of the reference plane if defined arbitrarily.

Example 1.4.1

An example to illustrate the calculation of the values of TTV, bow and warp is shown in Figure 1.7. The reference plane is taken at the midspan between between the probes A and B, as shown in Figure 1.7.

Solution:

The TTV of this wafer according to Equation (1.5) is

because the thickness happens to be the same throughout the wafer surface in this example. Normally, a non‐zero TTV is expected.

The bow of the wafer, , is measured at the center point of the wafer, and defined in Equation (1.6). It is

Since the bow is positive, the wafer is above the reference plane in a convex shape around the center. Note that the value of bow depends on the location of the reference plane. The measurements of bow, , at other points on the wafer are listed in the following table.

bow

2

0.3

The warp of this wafer can be determined by employing Equation (1.7). Since and , the warp is

Note that the value of warp is independent of the probe position relative to the wafer. However, change of the reference plane with respect to the wafer will affect the value of warp. Therefore, the TTV, bow and warp of the point at the center, shown in Figure 1.7, is:

If probe B in Figure 1.7 is shifted downward by four units, the measurements of the probe B, , will be added to by four units. In this case, the reference plane at the halfway point between the two probes will be at the level aligned with the back side of the wafer at the leftmost point. The values at each point can be recalculated and listed in Table 1.4.

Thus, the parameters of surface quality are

As expected, the values of TTV and warp do not change, while the value of bow changes. The change in the bow values is exactly two units, half of the shift in , as expected.

Figure 1.7 Example illustrating the calculation of TTV, bow and warp of a wafer, with the reference at the midspan between the two probes.

Table 1.4 Results of example in Figure 1.7 with probe B shifted downward by four units.

6

3

4.7

7

9

6

8

11

9.3

7

5

8

16

16

16

16

16

16

2

8

4.6

0

2

1

4

2.3

0

1

1.4.2 Discussion on Warp

As observed in the preceding example, the values of bow are affected by the position of the reference plane. In the standards [ASTM Standard F657 (1999); SEMI MF657 (2014)], a wafer is supported by three hemispherical points on a reference ring that establishes a reference plane. The gravity‐induced deflection will also affect the values of bow and warp. The standards in [ASTM Standard F1390 (2002); SEMI MF1390 (2018)] ratified such problems by defining warp with automated scanning. In the standards, the median surface is mathematically corrected for gravitational effects and for the mechanical signature of the instrument. A parameter, , is defined as the distance between the wafer median surface and the point halfway, at the midspan, between the upper and lower probes. See also Figure 1.5.

The position, , of the median surface of the wafer at each point with respect to a plane halfway between the upper and lower probes is, as discussed earlier,

which is the same as Equation (1.6). Gravitational and other compensations are applied to the ‐position of the median surface. A reference plane is then constructed by a least‐squares fit to the median surface ‐position data at all points of the scan pattern. The ‐value of the reference plane is called . The reference plane deviation (RPD) is defined as the difference between the measured ‐position, , and the reference, , at each point

A positive RPD at the center renders a dome‐shaped (or convex) wafer; while a negative RPD at the center renders a bowl‐shaped (or concave) wafer.

The warp is then defined as the difference between the largest and smallest of the RPD defined in Equation (1.9), by taking into consideration the signs of values,

Warp is akin to the potato‐chip effect and may be caused by residual stress internally or unequal stresses on the two exposed surfaces of the wafer, or aggravated by the gravity‐induced deformation and dynamics with inertia force of spinning the wafer for measurement. In recent years, different equipment and techniques have been developed, such as non‐dynamic whole‐surface metrology using the optical method [Wei and Kao (1999); Wei et al. (1998b)].